Caches and Address Translation. Consider a 64-byte cache with 8 byte blocks, an associativity of 2 and LRU block replacement. Virtual addresses are 16 bits. The cache is physically tagged. The processor has 16KB of physical memory.

(a) What is the total number of tag bits?

(b) Assuming there are no special provisions for avoiding synonyms, what is the minimum page size?

(c) Assume each page is 64 bytes. How large would a single-level page table be given that each page requires 4 protection bits, and entries must be an integral number of bytes.

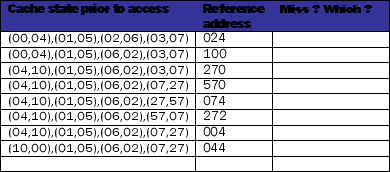

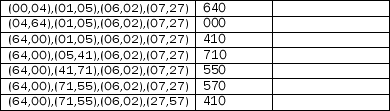

(d) For the following sequence of references, label the cache misses.Also, label each miss as being either a compulsory miss, a capacity miss, or a conflict miss. The addresses are given in octal (each digit represents 3 bits). Assume the cache initially contains block addresses: 000, 010, 020, 030, 040, 050, 060, and 070 which were accessed in that order

(e) Which of the following techniques are aimed at reducing the cost of a miss: dividing the current block into sub-blocks, a larger block size, the addition of a second level cache, the addition of a victim buffer, early restart with critical word first, a writeback buffer, skewed associativity, software prefetching, the use of a TLB, and multi-porting.

(e) Which of the following techniques are aimed at reducing the cost of a miss: dividing the current block into sub-blocks, a larger block size, the addition of a second level cache, the addition of a victim buffer, early restart with critical word first, a writeback buffer, skewed associativity, software prefetching, the use of a TLB, and multi-porting.

(f) Why are the first level caches usually split (instructions and data are in different caches) while the L2 is usually unified (instructions and data are both in the same cache)?

Definitions:

Expected Utility Function

A mathematical representation of an individual's preference for certain outcomes over others, considering the uncertainty of those outcomes.

Utility Function

A mathematical representation of a consumer’s preference ordering over a choice set, used to describe how consumers allocate their income to maximize their satisfaction.

Risk Neutral

An attitude or preference indicating indifference between choices with uncertain outcomes, focusing instead on the expected values.

Risk Averse

A characteristic of preferring to avoid risk, inclining towards guaranteed outcomes over potentially higher-yielding but uncertain ones.

Q2: <img src="https://d2lvgg3v3hfg70.cloudfront.net/TB2835/.jpg" alt=" A) 0

Q3: To append data to an existing file,

Q4: The reverse method is defined in the

Q6: Discuss the difference between under-constrained, fully constrained,

Q6: Use an orbital interaction diagram to provide

Q14: Internal dream refers to …

Q50: Define spline.

Q54: Write a systematic name for the following

Q90: Give the name and basic characteristics of

Q139: Describe chemical machining.