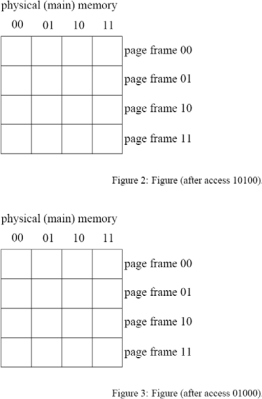

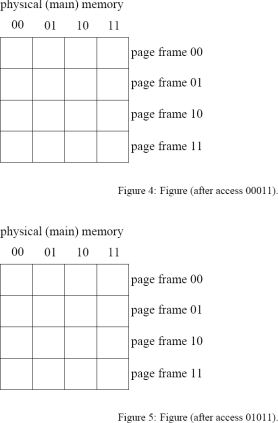

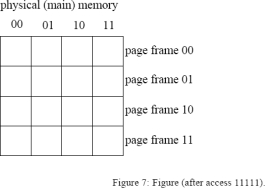

This question covers virtual memory access. Assume a 5-bit virtual address and a memory system that uses 4 bytes per page. The physical memory has 16 bytes (four page frames). The page table used is a one-level scheme that can be found in memory at the PTBR location. Initially the table indicates that no virtual pages have been mapped. Implementing a LRU page replacement algorithm, show the contents of physical memory after the following virtual accesses: 10100, 01000, 00011, 01011, 01011,11111. Show the contents of memory and the page table information after each access successfully completes in figures that follow. Also indicate when a page fault occurs. Each page table entry (PTE) is 1 byte.

Definitions:

Norms of Business

The accepted standards and practices that guide behavior in the business world.

Government Takeover

The acquisition of control over a company or sector by the government, potentially involving nationalization or requisition of private assets.

Per-Unit Costs

The expense incurred to produce, acquire, or sell one unit of a product or service, used in calculating profitability and pricing strategies.

Fixed Costs

Costs that do not vary with the volume of production or sales, such as rent, salaries, and insurance.

Q6: A competitive advantage has three characteristics: (fill

Q9: If you owned a company of 1,000

Q10: Memes are:<br>A) Comedians who express humor without

Q11: What is the average time to read

Q11: Fill in the code in Comparable_ c

Q13: Forwarding logic design. For this problem you

Q16: After the following program is finished, how

Q18: New experiments generate new _.

Q30: When is the zoning compartment of the

Q60: How many values can m<sub>l </sub>have for