Caches and Address Translation. Consider a 64-byte cache with 8 byte blocks, an associativity of 2 and LRU block replacement. Virtual addresses are 16 bits. The cache is physically tagged. The processor has 16KB of physical memory.

(a) What is the total number of tag bits?

(b) Assuming there are no special provisions for avoiding synonyms, what is the minimum page size?

(c) Assume each page is 64 bytes. How large would a single-level page table be given that each page requires 4 protection bits, and entries must be an integral number of bytes.

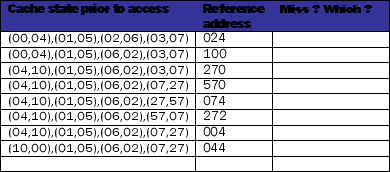

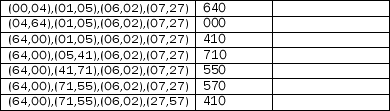

(d) For the following sequence of references, label the cache misses.Also, label each miss as being either a compulsory miss, a capacity miss, or a conflict miss. The addresses are given in octal (each digit represents 3 bits). Assume the cache initially contains block addresses: 000, 010, 020, 030, 040, 050, 060, and 070 which were accessed in that order

(e) Which of the following techniques are aimed at reducing the cost of a miss: dividing the current block into sub-blocks, a larger block size, the addition of a second level cache, the addition of a victim buffer, early restart with critical word first, a writeback buffer, skewed associativity, software prefetching, the use of a TLB, and multi-porting.

(e) Which of the following techniques are aimed at reducing the cost of a miss: dividing the current block into sub-blocks, a larger block size, the addition of a second level cache, the addition of a victim buffer, early restart with critical word first, a writeback buffer, skewed associativity, software prefetching, the use of a TLB, and multi-porting.

(f) Why are the first level caches usually split (instructions and data are in different caches) while the L2 is usually unified (instructions and data are both in the same cache)?

Definitions:

Backstabs

Acts of betrayal or disloyalty typically involving deceitful actions against someone who trusts the betrayer.

Productivity

The quantification of how effectively a human, device, manufacturing plant, or system transforms inputs into outputs that are beneficial.

Team Player

An individual who works well within a group, contributing effectively to achieve shared goals and objectives.

Emotional Support

Assistance provided by offering empathy, concern, affection, love, trust, acceptance, intimacy, encouragement, or caring.

Q2: Morality, legality, and ethics are basically the

Q4: Executives in the United Kingdom make a

Q5: What is the "dark side" of Level

Q8: What is the output of the following

Q12: Draw a BFS tree from the following

Q13: Which of the following choices lists the

Q14: What is the output for y? <br>int

Q23: What professional industry organization is dedicated to

Q28: Describe the general characteristics of a program

Q29: Draw the product of the following reaction.